## **Achieving Warpage**

CTE mismatch

between chip and substrate is the root cause for reliability issues in flip chip packages, such as excessive warpage, low dielectric layer cracksolder mask cracking, and bump cracking. The first and foremost thing in designing a flip chip package is to control excessive warpagevtorpraget the specification this paper, a cappetup chip package is proposed to control the warpwedeasto reduce the stress. In the pedie flip chip package tal cap tightly covers and bonds with the die through an adhesive material. As a result, the catheetotas a higher effective NCTE. adjusting the thicknesset of cap, the effective of the cappedie can metschwith the TCE of substrate, theoretically achievingwaepage or warfrageTo verify the concept far envarpage control, 45mmx45mm sizeappedieflip chip packasgelesigned and manufactubressed on the guidanceinfintene life ent modeling, where a coppoap dieth 0.4mm thickness is selected. The hadow Moire test is performed to measure the warpage function of temperatures from 260 c. Experimental data show that in them to be range the warpage curve of the cappelide package is almost flatJ ET BT 1 0 0 1 259.61636(ce)-3(p)-5(t)-302(f)45.7

Bare Die FCBGA

(b)

FCBGA with Stiffener Ring

warpageIn Figure 2, (a), (b) and (c) show the basic assembly ethod, which will introduce an additional stress into the steps of a flip chip package, whehe tstep (a) is fodie attach package.

process, the step (b)is for underfill dispensing and curing process, and the step (cm) (d) is for stiffener/lid attachment process. After the die atta**st**ep (a), the electrical connection between the die and substrate Iboosen completed and the warpage at this point is small due to the quick relaxation of the solder bump stress that is caused by the violatic property of the solder materialn other words, the die attachstep (a) completes the electrical connection between the die an substrate, but the mechanical connection is werakurder to enhance the walk mechanical connection protect the solder bumps, the underfill is filled into the gap between the die and substrate. Sohe application of underfill in the step (b) is only for the reliability of the electrical connection from the mechanical viewpointThe underfill is usually wered at a high temperature, such a \$5 C. The flip chip package during the underfill curing process is very flat, i.ethe warpage at the point is very small due to the same reason as the voltagetic property of the solder material. However, after the underfill is cured, the die and substrate are strongly connected mechanical viewpointThen, when cooling down to the room temp or rising up to the reflow temperature, the warpage will be developed due to the big CTE differencebetween the die and substrate of example the downwards warpage at room Capped Die Flip chip Package Design temperature (also called coplanaristrue) is shown in Figure 2 (b). JEDEC specification has defind@mil or 200um for large flip chip packageas the tolerance limit. However, far 45mmx45mm size of flip chip package bare die FCBGA can have a warpagever 12mil or 300um. The excessive shownin Figure 3, and an assembly processappeedie flip process, failures during package functional testreduce the the next processing step after underfill curing process, die, (d) covering the die cap onto the die, and (abnourrently showed in Figure 1 (b) or (c). The mechanism of using auring theunderfill and adhesive materials. stiffener or lid to reduce the warpage is illustrated in Figure 2 (c) and (d) where the stiffener or lid applies a force torque it is seenthat theconventionalways using a stiffener or lid to mainly constrain the die, forming cappeddie, or says it is a reduce the warpage is a way tedieform the substrate, or saysdie control method, and the second is thathe underfill the flip chip package rises when the substrate-istefermed by the siffener or lid. For example, of the FCBGA with for the package types of bare dietiffener and lid, respectively. Though the Lidded FCBGAgives the lowest warpage, it causes highest stress in package, as compared ive a good joint of both underfill and adhesiven aterials at the bare die and stiffener packages.

In summary there are three point about the warpage control by using stiffener or lithat need to be keptin mind: (1) warpage habeendeveloped after underfill dispering and curing process. This means the transpage has been frozen in the package(2) stiffener or lid attachprocess is done after underfill curing processand (3) the conventional ways using stiffener or lid to control warpage is only to redeform the substrate Therefore, the above methods are substraterol

Figure 2. Assembly processes this chip package and mechanism of conventionalways for wapage control: (a) die attactb) undefill dispensingand curing, and (c) Stiffener or lattach

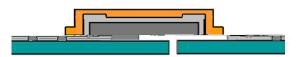

A cappeddie flip chip package is designed based on the preceding analysis for the mechanism of warpage@ally the three points of conventional warpage control mechanism. which includes a structure of cambdie flip chip package as warpage may cause a lot of issues in board level of operations, package as shown in Figure 4. The assembly process of such as solder ball bridging or opening during surface mourappeddie flip chip packages includes these steps) (a dispensing underfill material into the gaptween the die and warpage, a stiffener ring or a lid is conventionally applied in ubstrate, (b dispensing adhesive material on the top of the

It is seen that there are two key differencethefcapped die flip chip package designment the conventional flip chip at the edge of the substrate, forcing it to deform upwards. Sackages using stiffener or lidthe first one is that the die cap it is a substrate control method. As a result, the stress level material between the die and the substrate and the adhesive material between the die cap and die are concurrently cured. As a result the CTE between the apped die ant the substrate 45mmx45mm substrate size and 23mmx23mm die size, they get matched, and the warpage after the underfill warpage at room temperature are about 12mil, 8mil and 5mispensing and curing press as showed in Figure 2(b) may been avoidedbefore it is frozen in the package if a die cap with a proper thikness is selected. The same base resin can the die edge region.

Figure 3.A cappeddie flip chip package

Figure 4. Assembly process for cappedie flip chip package.

Some potentialfailure modes of appeddie flip chip packages are illutrated in Figure .5 The reason for the possible failure modes is that a high stress may take place around the die edge regiowhen the die caponstrains the deformation of the die during temperature change. Based on this consideration, an improved diepcies designed to lessen the risk of the failure modes. The capputed flip chip packages usig an improved die cap is shown in Figure 6

Figure 5 Potentialfailure modes for cappedie flip chip package

Figure 6 A cappeddie flip chip packagesing an improvedid cap design.

It is suggested than adhesive material should have the same Tg as that of the underfill material so that both materials consistently become softer or harder when temptere passes Tg. It is preferred than their fillers may be different. For

under application or test loading conditions, improving the reliability of bumps and lowk layers of the package.

Finally, it is explained why the cappetite package ets stable at the small warpage value 65 thm fact, the warpage value is the warpage of the flip chip package at curing temperature 65 C. It is seen from Figure 8 that the bare die package is just having the warpage value around the temperature. The warpe value of the capped die package no

Figure 10B.Contour plotof the deformation of the medium size of package at room and high temperatures.

Figure 10C.Contour plot of the deformation of the small size of package at room and high temperatures.

## (3) Effect of the thickness of die cap

In the preceding sectin for achieving warpagteee packaging the die cap titckness is selected by trial and error method through multiplerounds of simulations. Here, an interesting phenomenon, called/eo-controlled warpage is shown about warpageontrol by cappedlie when athicker die cap is selected to the simulation example, the same big package is used, but a thinner substrate core, 0.4mm thickness of core is considered. It has been seen that for 0.8mm thickness of core, 0.4mm thickness of die cap gives an ideal warpage control. The simulation shows a phenomenon of over-controlled warpage by the same 0.4mm thickness of die cap for the package the thinner core, as shown Figure 11(b). For the thin core, a thinner die cap, i.e., a 0.3mm thickness of die cap is propter an ideal warpage control, as shown in Figure 11(c). Note that the conventional stiffener and lid 0.0-5(w)23(1071a)-269(0)-5(x)-2(3)-4(x)-26(BT 1.0.0.14)

and lid 0 0-5(w)23(1071a )-269(0)-5(.)-2(3)-4( )-26( BT 1 0 0 1 48-4( )-26( BT 1 0 0 1 48-4(p//P << /MCa )-269(0(iv)7(es )T 1 0 07(

Figure 12. Contour plot of the deformation of big package using 8 layers of coreless substrate atmostemperatures.

Figure 13. Contour plot of the deformation of small package using 6 layers of coreless substrate at room temperatures.

## Conclusions

The experimental and simulation results show that warpagefree packaging in the full range of the perature variation can be achieved by using capplied flip chip package design flore experimental studies about the capped die flip chip package design are needed, especially for its possible failure modes ome major design considerations include the election of adhesive material for bonding the die cap with the diea proper thickness of die cap, and a proper gap between the die cap side and the die edge. The assembly process needs to be carefully performed to avoid the voids between the die cap and the die because both adhesive and